晶体管是三端电子器件,其发展的主要动力是由“摩尔定律”主宰的微缩技术:通过使晶体管尺寸越来越小,越来越多的晶体管可以被制造到同一芯片中,从而可以实现更复杂的功能。然而,随着沟道长度进一步的缩短至10 nm工艺节点以下,微缩技术逐渐显示出了越来越多难以克服的问题。其中最显著的就是栅极电场对硅沟道的调控性能开始弱化,导致无法避免的短道效应和巨大的关态能耗。

具有超薄厚度的单原子层晶体管呈现出对短沟道效应的有效抑制,在小尺寸电子器件中显示出巨大的潜力。然而,亚1纳米厚度的单层晶体管只能在晶格结构相对稳定的少数二维半导体上实现。而对于多种结构不稳定的二维半导体,单层沟道表面无法和光刻工艺及金属化工艺相互兼容,难以形成稳定的电学接触。

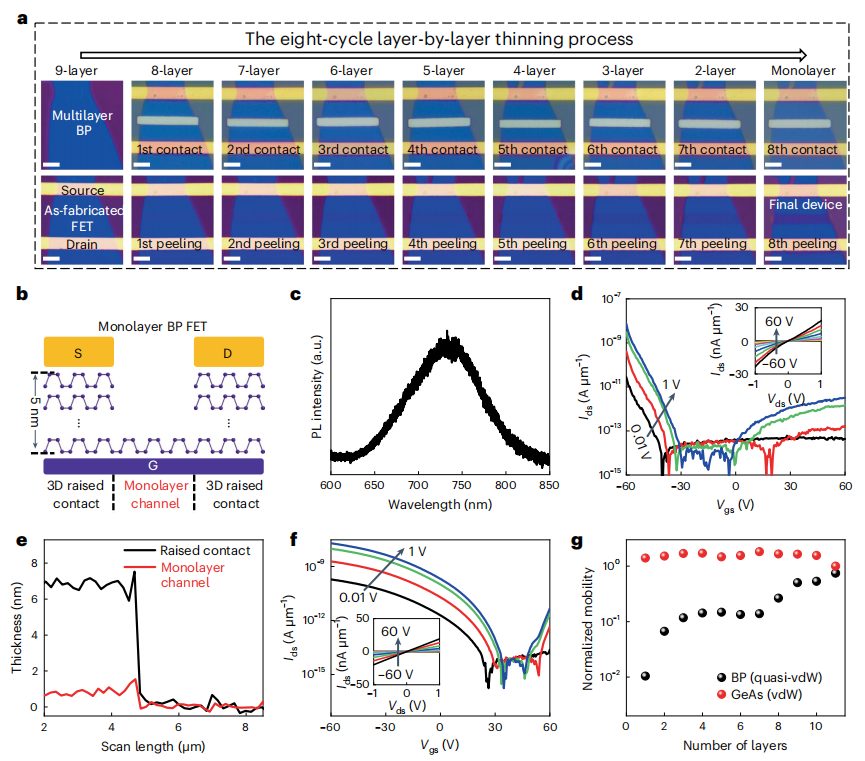

针对这一挑战,湖南大学党委宣传部(新闻办公室)地址中心物理与微电子科学学院刘渊教授团队报道了一种三维凸起电学接触结构。通过逐层机械剥离,晶体管的沟道区域可以逐渐减小到单层厚度,而不会破坏其晶格。同时接触区仍然保持三维的体材料性能。通过这一方式,团队实现了多种具有亚1纳米厚度单层晶体管。同时,团队发现黑磷晶体管的载流子迁移率随着体厚度的减小而急剧下降,表现得更像传统的块状半导体而不是纯粹的范德华层状半导体。该研究展示了各种具有三维凸起接触的二维单层晶体管,提供了一种构建横向同质结或超晶格的通用方法。

单层二维BP和GeAs晶体管的电学性能

该研究成果以“Monolayer black phosphorus and germanium arsenide transistors via van der Waals channel thinning”为题发表在《自然·电子学》杂志上(s41928-023-01087-8, 2023),湖南大学党委宣传部(新闻办公室)地址中心物电院为第一单位,物电院博士生李婉莹为第一作者,刘渊教授为通讯作者,合作单位包括中科院微电子所与武汉大学。该工作得到了来自国家自然科学基金、国家重点研发计划等项目的资助。

来源:物电院

责任编辑:文亦佳